Product Summary

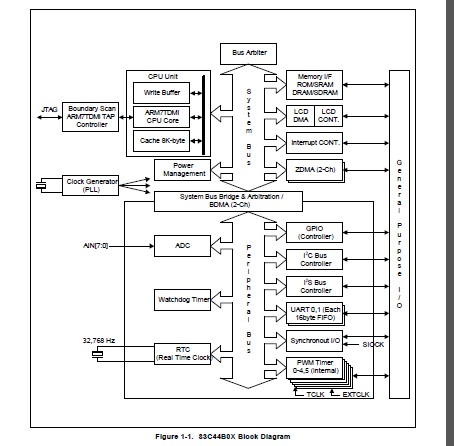

The S3C44BOX01L is a risc microprocessor. It is designed to provide a cost-effective and high performance micro-controller solution for hand-held devices and general applications. To reduce total system cost, S3C44BOX01L also provides the following: 8KB cache, optional internal SRAM, LCD controller, 2 channel UART with handshake, 4-channel DMA, System manager (chip select logic, FP/ EDO/SDRAM controller), 5-channel timers with PWM, I/O ports, RTC, 8-channel 10-bit ADC, IIC-BUS interface, IIS-BUS interface, Sync. SIO interface and PLL for clock. The S3C44BOX01L was developed using a ARM7TDMI core, 0.25 um CMOS standard cells, and a memory compiler. Its low-power, simple, elegant and fully static design is particularly suitable for cost-sensitive and power sensitive applications. Also S3C44B0X adopts a new bus architecture, SAMBA II (SAMSUNG ARM CPU embedded Microcontroller Bus Architecture). An outstanding feature of the S3C44B0X is its CPU core, a 16/32-bit ARM7TDMI RISC processor (66MHz) designed by Advanced RISC Machines, Ltd. The architectural enhancements of ARM7TDMI include the Thumb decompressor, an on-chip ICE breaker debug support, and a 32-bit hardware multiplier.

Parametrics

S3C44BOX01L absolute maximum ratings: (1)VDD DC Supply Voltage: 3.6 V; (2)VIN DC Input Voltage: 3.3 V Input buffer, 4.6 V; (3)VOUT DC Input Voltage: 3.3 V buffer, 4.6 V; (4)Ilatch Latch-up Current: ± 200 mA; (5)TSTG Storage Temperature: - 40 to 125 ℃.

Features

S3C44BOX01L features: (1) Architecture: Integrated system for hand-held devices and general embedded applications, 16/32-Bit RISC architecture and powerful instruction set with ARM7TDMI CPU core. Thumb de-compressor maximizes code density while maintaining performance. On-chip ICEbreaker debug support with JTAGbased debugging solution. 32x8 bit hardware multiplier. New bus architecture to implement Low-Power SAMBA II(SAMSUNG ARM CPU embedded Micro-controller Bus Architecture); (2) Cache Memory & internal SRAM: 4-way set associative ID(Unified)-cache with 8Kbyte. The 0/4/8 Kbytes internal SRAM using unused cache memory. Pseudo LRU(Least Recently Used)Replace Algorithm. Write through policy to maintain the coherence between main memory and cache content. Write buffer with four depth. Request data first fill technique when cache miss occurs.

Diagrams

|

S3C44B0X |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

S3C4510B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

S3C4530A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

S3C49F9X |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))